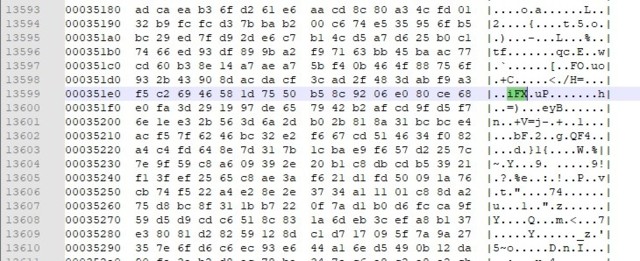

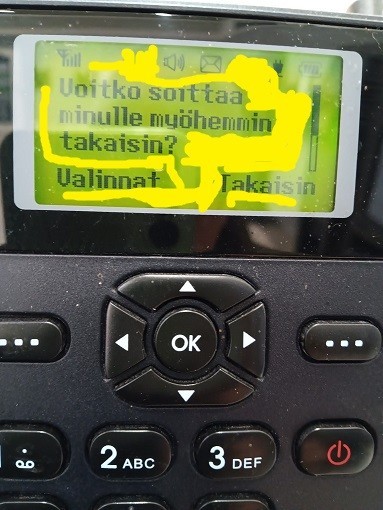

Linux cmds head, xxd and hexdump

keskiviikko, 24. huhtikuu 2024

Linux cmds head, xxd and hexdump

sunnuntai, 21. huhtikuu 2024

Helvar lighting system, one can try Helvar apps ....

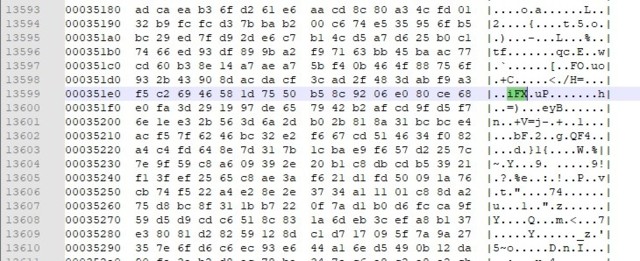

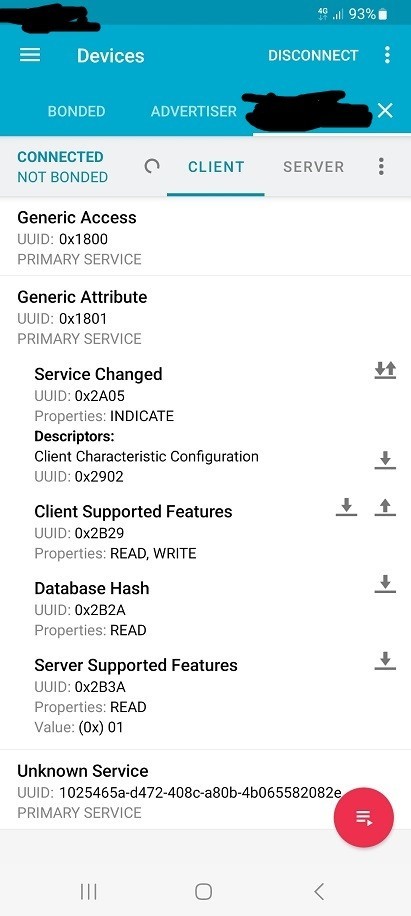

Unknown IoT system

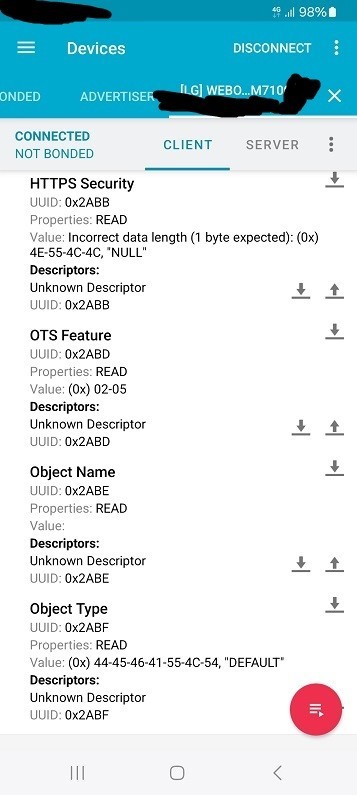

Bottle returning automaton machine telephone system

torstai, 28. maaliskuu 2024

6+HOLD+POWER LCD pixel test

4+HOLD+POWER Close Call test

5+HOLD+POWER USB port test

7+HOLD+POWER Load test data

1+7+POWER Battery save test

3+HOLD+POWER Display contrast

2+5+9+POWER Firmware version

3+9+POWER Scan test

6+LO+POWER Boot mode for flashing firmware

3+0+POWER Key touch test

2+7+POWER Battery charge test

1+0+POWER All memory clear

lauantai, 23. maaliskuu 2024

To activate Close Call test mode, turn off scanner and press 4 + HOLD + POWER.

In CC test mode PWR remote command returns

xxx, 00000000 (xxx = signal strength value) whether there is CC hit or not

SLS and GLG commands return LCD screen info/reception status ok.

lauantai, 9. maaliskuu 2024

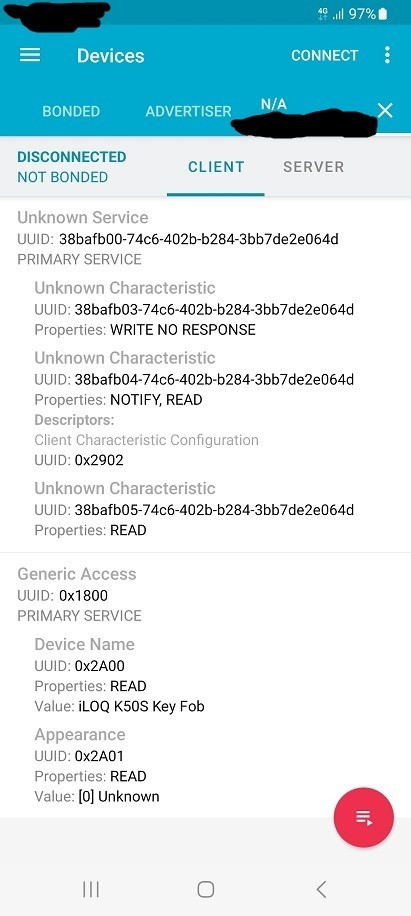

iLOQ keyfob ... requesting pairing ...

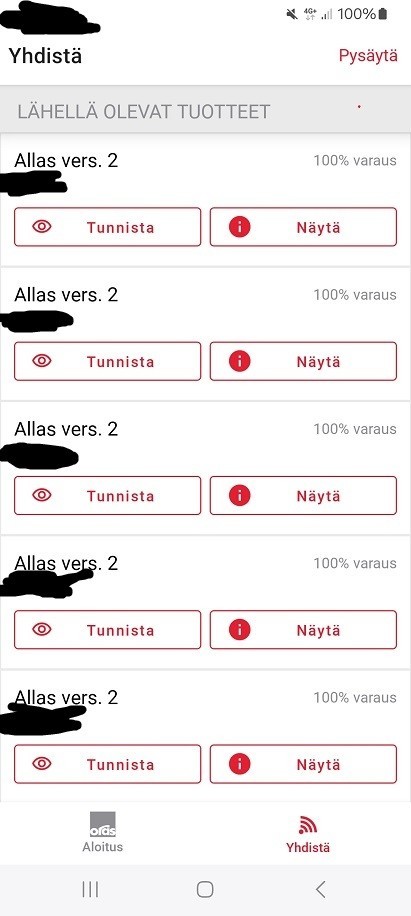

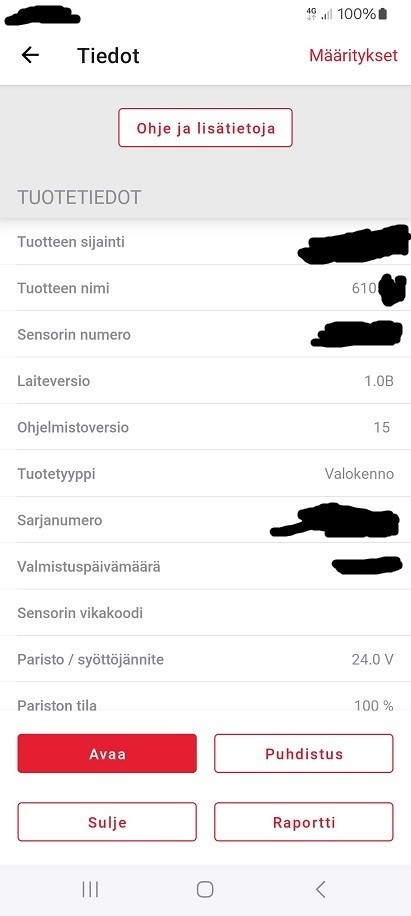

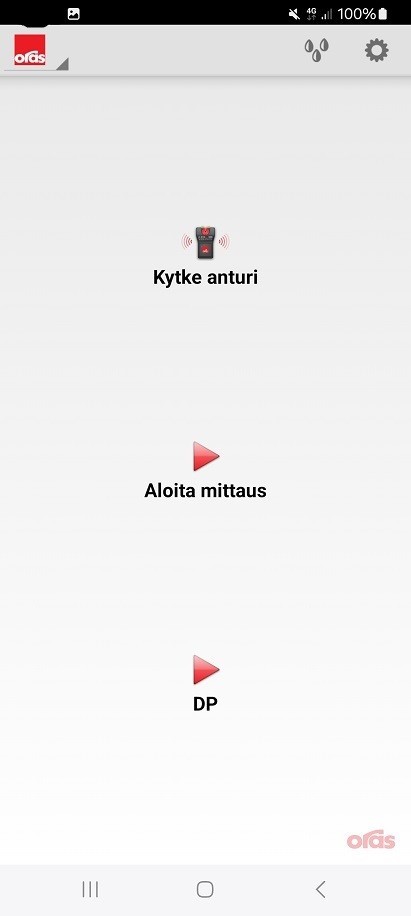

Oras apps

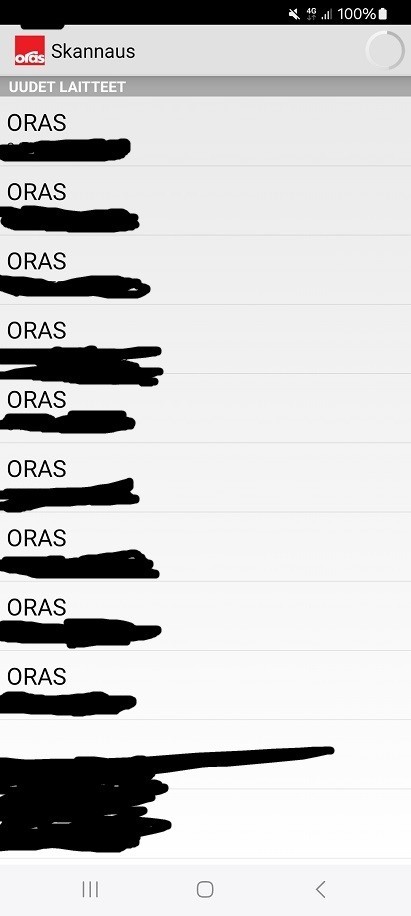

Unknown ... but in interesting places ...

1200 18.04 1PN34 20.04 4-FSK 433 450 462.325 590nm 730nm 8325137772292692867 850 nm 850nm 868 950nm ABAX AD8310 ADALM-PLUTO AFSK ALAM AOR AOS APRS AR-IR ARtiming ASA ASK ASSA AT-878 AX2012 Aceco ActiveGPS Aiptek Airthings Akkulaturi Amplifier Analog Android Anytone App Application Arduino Argmax Aruba Audacity Audio BDW BEHA BG20 BLE BR330T BT-AP Beacon Bing Bluetooth Bobrikloader C Sharp C# CAM CC Debugger CC1101 CC1120 CC308 CC3300 CC780 CC785 CCIR CCRF3 CDC CFM CIR COM CORDIC CPL CTCSS CTEK CURL Cam Camera Close Call Cmd Console Continuous Controller DAC DCS DDK6 DECT DIO5 DMR DPPM DSC DSC-H9 DSDPlus DSP DTMF DUMP Daikin Data Debug Deco Devices Didymium Digikamera Doorbell Dragino Due EDENRED EEPROM EIRP EasyScanner Ensto Event FAX FFT FSK Festival Fiddler Filter Fire-Out Firmware Fleet Framework Frogblue G-Smart GMDSS GNU Radio GNURadio GPIO GPS GR-IIO GSM Grundfos HAMA R8 HDR HMSOFT Hopealiima Hoya I/Q IIO IIS ILSpy IOC 576 IOCFG IOT IPP350 IQFILE IR laser ISM Info-TV Infrapuna Intelligence Inversion IoT Key LUMIA 532 Log Lora LoraWAN Lämpökamera MQTT MSK Matplotlib Mobitex Mods MultiPSK Multimon-ng NET NET6 NET7 NFC NIR NMEA Numpy OOK ORAS OpenCV PDU PNB586 POCSAG PWM Pager Pandas Peltipoliisi Plug-in Plugin PulseView Puuvilla Python RAW RDS RFAnalyzer RGBCam RS232 RSSI RTL-SDR Radiomodem Rdsspy Receive Remote Retekess Reverse engineering Ride Robot SDK SDR SDRSharp SDS SX1278 SX127x Scan Scanner Scipy ScopeView Seek Thermal Semtech Serial Sharepoint Silvercrest SmartRF04eb SmartRFStudio SpectraCam Speed Surveillance Sync TCP TETRA Tag Thermal Tone Transmit UBC-3500XLT UDT-4 URH USB Ubuntu Uniden Uno VB-Audio VIdeo Valonvahvistin Verto VirtualBox Visual Studio WAVEFORM Win10 Windows Windows Phone Wireless Wireshark XMLRPC ZWB1 dotPeek openCV pyadi-iio pylibiio