Dragino Lora Module (Semtech SX1278)

SX1278 library https://github.com/open-electronics/LoRa/releases

#include <SX1278.h>

#define SERIAL_SPEED 9600

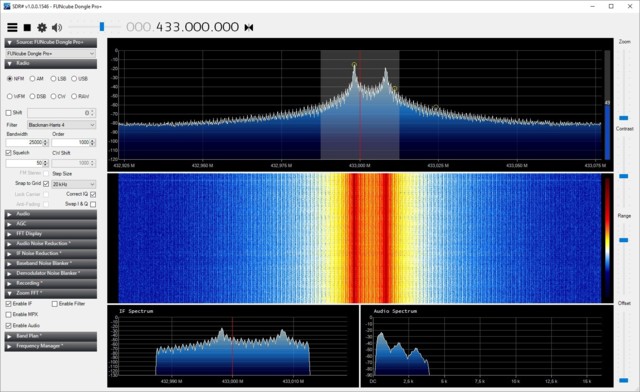

#define FREQ 433

#define BPS 1200

#define STATE_STANDBY 1

#define STATE_FSTX 2

#define STATE_TX 3

#define S_DELAY 1

#define L_DELAY 10

#define NUM_SYNC_BYTES 3

#define TX_BUFFER_LEN 255

#define SX_BEGIN "SX.begin"

#define SX_BITRATE "SX.readBPS "

#define SX_FREQ "SX.readFreq "

#define RegRxBw 0x12

#define RegPacketConfig1 0x30

byte syncBytes[NUM_SYNC_BYTES] = {0x01, 0x01, 0x01};

byte txBuffer[TX_BUFFER_LEN];

void setup() {

Serial.begin(SERIAL_SPEED);

if (SX.begin()) {

Serial.println(F(SX_BEGIN));

delay(S_DELAY);

SX.startModeFSKOOK();

SX.setModulation(0); // FSK

// Channel filter bandwidth control. RxBwMant (bits 4-3): 01->20 & RxBwExp (bits 2-0): 4 = 25 kHz

byte b = SX.SPIread(RegRxBw);

bitClear(b, 4);

bitSet(b, 3);

bitSet(b, 2);

bitClear(b, 1);

bitClear(b, 0);

SX.SPIwrite(RegRxBw, b);

SX.setFreq(FREQ);

Serial.print(F(SX_FREQ));

Serial.println(SX.readFreq(), DEC);

SX.setBPS(BPS);

Serial.print(F(SX_BITRATE));

Serial.println(SX.readBPS(), DEC);

// Set preamble length & polarity, 0=0xAA, 1=0x55

SX.setPreamble(3, 0);

SX.setSync(1, syncBytes, NUM_SYNC_BYTES);

SX.setPacket(0, 0, 16); // fix len, no crc, len 16

// Defines DC-free encoding/decoding performed: 00->none, 01->manchester, 10->whitening

b = SX.SPIread(RegPacketConfig1);

bitClear(b, 6);

bitClear(b, 5);

SX.SPIwrite(RegPacketConfig1, b);

SX.setState(STATE_STANDBY);

delay(S_DELAY);

SX.setPackNoPack(1); // Set packet mode

// RegOokPeak (0x14). Bit 5, enables the Bit Synchronizer: 0 -> bit sync disabled (not possible in packet mode, 1 -> //bit sync enabled

SX.setBitSync(1);

SX.setPower(1); // 5 mW

for (int i = 0; i < TX_BUFFER_LEN; i++) {

txBuffer[i] = i;

}

SX.setState(STATE_STANDBY);

SX.setState(STATE_FSTX);

delay(S_DELAY);

SX.setState(STATE_TX);

delay(L_DELAY);

}

}

void loop() {

SX.dataToSend(txBuffer, TX_BUFFER_LEN);

delay(L_DELAY);

}

Kommentit

Tämän blogin kommentit tarkistetaan ennen julkaisua.