WX station 433 MHz OOK remote sensor, channel change signal.

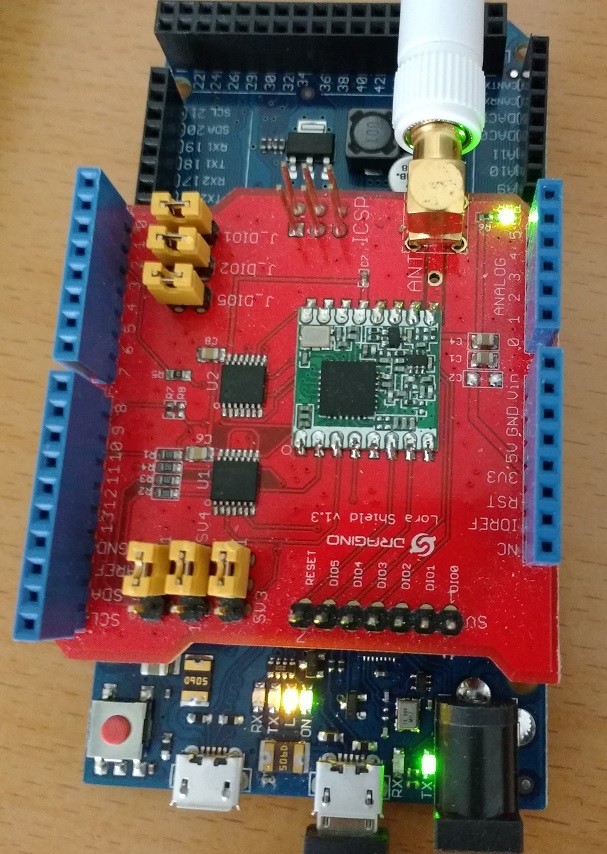

Arduino Due & Dragino 433 MHz Lora Shield (Semtech SX1278).

#include <SPI.h>

#define SERIAL_SPEED 38400

#define FREQ 433.983

#define BPS 1800

#define STATE_SLEEP 0

#define STATE_STANDBY 1

#define STATE_FSRX 4

#define STATE_RX 5

#define S_DELAY 10

#define L_DELAY 100

#define SX_FREQ "Frequency "

#define SX_VERSION "Version code of the chip "

#define SX_RX "RX..."

#define RCS_RX "Received "

#define RCS_SEP " / "

#define RCS_UNKNOWN_ENC "Unknown encoding"

#define RCS_BIT "bit "

#define RCS_PROTOCOL "Protocol: "

#define CH_FILTER_BW B00001100 // 25 kHz

#define DATA_PIN 7

#define RegFifo 0x00

#define RegOpMode 0x01

#define RegBitrateMsb 0x02

#define RegBitrateLsb 0x03

#define RegFrfMsb 0x06

#define RegFrfMid 0x07

#define RegFrfLsb 0x08

#define RegPaRamp 0x0a

#define RegRssiConfig 0x0e

#define RegRssiThresh 0x10

#define RegRxBw 0x12

#define RegOokPeak 0x14

#define RegPreambleDetect 0x1f

#define RegSyncConfig 0x27

#define RegPacketConfig1 0x30

#define RegPacketConfig2 0x31

#define RegPayloadLength 0x32

#define RegIrqFlags2 0x3f

#define RegDioMapping1 0x40

#define RegVersion 0x42

#define SX_OSC_FREQ 32000000

#define SX_RESET 9

#define SX_RESET_DELAY_H 5

#define SX_RESET_DELAY_L 100

#define SPI_SS 10

#define SPI_RW_DELAY 50

volatile uint32_t pulse_len = 0;

void setup() {

Serial.begin(SERIAL_SPEED);

if (initSX()) {

pinMode(DATA_PIN, INPUT);

Serial.print(F(SX_VERSION));

Serial.print(readSPI(RegVersion));

Serial.println();

delay(S_DELAY);

startFSK();

// Set OOK

uint8_t b = readSPI(RegOpMode);

bitClear(b, 6);

bitSet(b, 5);

writeSPI(RegOpMode, b);

// Channel filter bandwidth control

writeSPI(RegRxBw, CH_FILTER_BW);

setFreq(FREQ);

Serial.print(F(SX_FREQ));

Serial.println(FREQ, DEC);

setBps(BPS);

// Bits 7-6: AutoRestartRxMode, 01 On, without waiting for the PLL to re-lock

// Bit 4: Enables the Sync word generation and detection: 0 => Off, 1 => On

// Bit 5: Sets the polarity of the Preamble. 0 0xAA, 1 0x55

// Bits 2-0: Size of the Sync word (SyncSize + 1)

b = readSPI(RegSyncConfig);

bitClear(b, 7);

bitSet(b, 6);

bitClear(b, 4);

bitClear(b, 5);

writeSPI(RegSyncConfig, b);

// Bits 6-5: Defines DC-free encoding/decoding performed: 00->none, 01->manchester, 10->whitening

// Bit 7: packet format, 0 = fixed length, 1 = variable length

// Bit 4: crc calc/check, 0 = off, 1 = on

// Bits 2-1: Defines address based filtering in Rx: 00 ïƒ None (Off)

// Bit 3: Defines the behavior of the packet handler when CRC check fails:

// 0 => Clear FIFO and restart new packet reception. No PayloadReady interrupt issued.

// 1 => Do not clear FIFO. PayloadReady interrupt issued.

// Bit 0: Selects the CRC and whitening algorithms:

// 0 CCITT CRC implementation with standard whitening

// 1 IBM CRC implementation with alternate whitening

writeSPI(RegPacketConfig1, 0);

// Data processing mode: 0 => Continuous mode, 1 => Packet mode

b = readSPI(RegPacketConfig2);

bitClear(b, 6);

writeSPI(RegPacketConfig2, b);

// Set DIO mapping

b = readSPI(RegDioMapping1);

bitClear(b, 5);

bitClear(b, 4);

bitClear(b, 3);

bitClear(b, 2);

writeSPI(RegDioMapping1, b);

// Bit 5: enables the Bit Synchronizer:

// 0 -> bit sync disabled (not possible in packet mode), 1 -> bit sync enabled

b = readSPI(RegOokPeak);

bitClear(b, 5);

writeSPI(RegOokPeak, b);

// RegPreambleDetect (0x1f). Enables Preamble detector when set to 1.

// The AGC settings supersede this bit during the startup / AGC phase.

// Bit 7: 0 -> turned off, 1 -> turned on

// Bits 6-5: Number of Preamble bytes to detect to trigger an interrupt.

// 00 1 byte, 10 3 bytes, 01 2 bytes

b = readSPI(RegPreambleDetect);

bitClear(b, 7);

writeSPI(RegPreambleDetect, b);

clearFifoAndFlags();

setState(STATE_FSRX);

delay(L_DELAY);

setState(STATE_RX);

delay(S_DELAY);

Serial.println(F(SX_RX));

attachInterrupt(digitalPinToInterrupt(DATA_PIN), isr, CHANGE);

}

}

void loop() {

if ((pulse_len > 500) && (pulse_len < 3000)) {

Serial.println(pulse_len);

}

}

void isr() {

static uint32_t last_irq_ti = 0;

uint32_t t = micros();

pulse_len = t - last_irq_ti;

last_irq_ti = t;

}

void clearFifoAndFlags() {

// Flag(s) and FIFO are cleared when this bit is set

uint8_t b = readSPI(RegIrqFlags2);

bitSet(b, 4);

writeSPI(RegIrqFlags2, b);

delay(S_DELAY);

}

void setBps(uint16_t bps) {

uint16_t baudRate = SX_OSC_FREQ / bps;

writeSPI(RegBitrateMsb, baudRate >> 8);

writeSPI(RegBitrateLsb, baudRate & 0xff);

}

void setFreq(float f)

{

uint32_t lf = (f * 1000000) / 61.035;

writeSPI(RegFrfMsb, (lf >> 16) & 0xff);

writeSPI(RegFrfMid, (lf >> 8) & 0xff);

writeSPI(RegFrfLsb, lf & 0xff);

}

void setState(uint8_t s) {

uint8_t b = readSPI(RegOpMode);

b = b | s;

writeSPI(RegOpMode, b);

}

void startFSK()

{

setState(STATE_SLEEP);

delay(S_DELAY);

uint8_t b = readSPI(RegOpMode);

bitClear(b, 7);

writeSPI(RegOpMode, b);

}

bool initSX() {

pinMode(SX_RESET, OUTPUT);

resetSX();

initSPI();

if (readSPI(RegVersion) == 0) {

return false;

}

setState(STATE_STANDBY);

return true;

}

void resetSX() {

digitalWrite(SX_RESET, LOW);

delayMicroseconds(SX_RESET_DELAY_L);

digitalWrite(SX_RESET, HIGH);

delay(SX_RESET_DELAY_H);

}

uint8_t readSPI(uint8_t addr) {

digitalWrite(SPI_SS, LOW);

SPI.transfer(addr);

delayMicroseconds(SPI_RW_DELAY);

uint8_t v = SPI.transfer(0x00);

digitalWrite(SPI_SS, HIGH);

return v;

}

void writeSPI(uint8_t addr, uint8_t v) {

digitalWrite(SPI_SS, LOW);

SPI.transfer(addr | 0x80);

delayMicroseconds(SPI_RW_DELAY);

SPI.transfer(v);

digitalWrite(SPI_SS, HIGH);

}

void initSPI()

{

digitalWrite(SPI_SS, HIGH);

pinMode(SPI_SS, OUTPUT);

SPI.begin();

SPI.setDataMode(SPI_MODE0);

SPI.setBitOrder(MSBFIRST);

}

Kommentit

Tämän blogin kommentit tarkistetaan ennen julkaisua.